△

爱上电苑 从电光火时开始

W e c h a t : d q x y d g h s

纸上得来终觉浅

绝知此事要躬行

电工电子培训第八弹

让我们一起开始项目实战学习

设计并制作一个

逻辑状态测试笔和多数表决器电路吧

培训时间:4月21日 3:00-4:00

培训地点:云塘工一A210

授课老师:袁志辉老师

项目总述

Part.01

项目描述

逻辑状态测试笔:本项目制作的逻辑状态测试笔,由集成门电路芯片74HC00、发光二极管、电阻等元器件组成,项目相关知识点有:基本逻辑运算、基本门电路、集成逻辑门电路等。

多数表决器:本项目是以组合逻辑电路的设计方法,用基本门电路的组合来完成具有多数表决功能的电路。

Part.02

项目要求

逻辑状态测试笔:

用集成门电路74HC00制作简易逻辑状态测试笔。要求测 试逻辑高电平时,红色发光二极管亮,测试逻辑低电平时,绿色发光二极管亮。

三人表决器:

用基本集成门电路设计制作三人表决器,3人中至少有2人同意,提案通过,否则提案不通过。

当表决某项提案时,同意则按下对应的开关,不同意则不按。表决结果用LED灯显示,如果灯亮,则提案通过,不通过LED灯不亮。

理论知识

Part.01

与或非运算

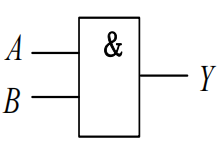

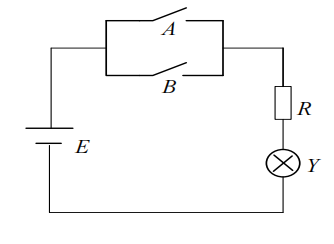

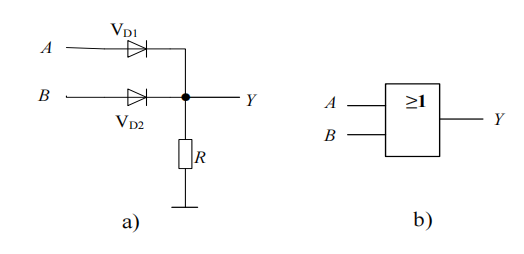

(1)与运算

◼ 当决定某一事件的所有条件都满足,该事件才发生,这种因果关系叫与逻辑关系,也称与运算或者称逻辑乘。

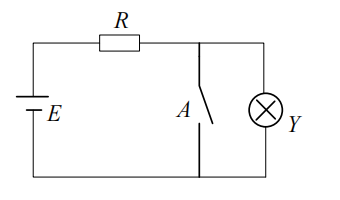

◼ 与运算对应的逻辑电路可以用两个串联开关A、B控制电灯Y的亮和灭来示意,如图所示。若用1代表开关闭合和灯亮。用0代表开关断开和灯灭。

◼ 由真值表可以将与门电路的逻辑功能归纳为:“有 0出0,全l出1”。

◼ Y和A、B的关系可以用下式表示Y = A*B

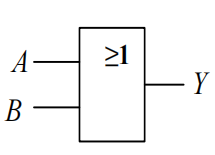

(2)或运算

◼ 决定某一事件的所有条件中,只要满足一个条件,则该事件就发生,这种因果关系称为或逻辑关系,也称或运算或者称为逻辑加。

◼ 或运算对应的逻辑电路可以用两个并联开关A、B控制电灯Y的亮和灭来示意。

◼ 若仍用1代表开关闭合和灯亮,用0代表开关断开和灯灭,电路的功能可以描述为:只要A、B两个开关中至少有一个闭合时,电灯Y就亮;否则,灯就灭。

◼ 或运算的逻辑表达式为 Y=A+B

◼ 对于多变量的或运算可用下式表示:

Y = A+ B +C +L

◼或门的逻辑功能:“有1出l,全0出0”。

(3)非运算

◼ 非运算表示这样的逻辑关系,当某一条件具备了,事件便不会发生,而当此条件不具备时,事件一定发生。

◼ Y和A之间的关系可用下式表示 Y = A。

◼ 逻辑功能:“有0出1,全1出0”。

◼ 逻辑关系示意图:

Part.02

分立元件门电路

(1)二极管门电路

◼ 二极管的开关特性

由于二极管具有单向导电性,即外加正向电压时导通,外加反向电压时截止,所以它在电路中相当于一个受外加电压极性控制的开关。

◼ 开启时间

二极管由反向截止转换为正向导通所需要的时间称为开启时间。

◼ 关断时间

二极管由正向导通转换为反向截止所需要的时间称为关断时间。

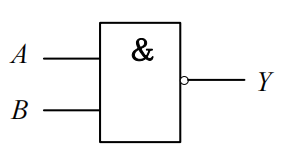

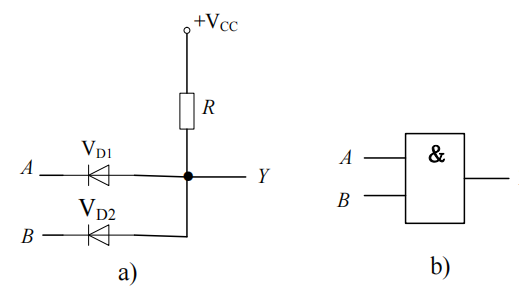

◼二极管门电路逻辑图:

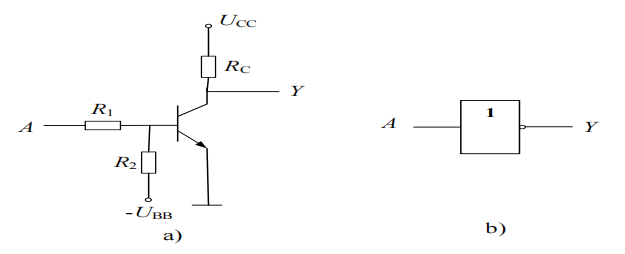

(2)三极管门电路

◼ 三极管的开关特性

1、三极管在截止与饱和导通两种状态间迅速转换时,二极管PN结的结电容使得内部电的建立和消散都需要一定的时间。

2、当输入信号电压由低电平跳变到高电平时,三极管由截止到饱和导通所需要时间,为开启时间, 用ton表示;

3、当输入信号电压由高电平跳变到低电平时,三极管由饱和导通到截止所需要时间,为关断时间,用toff表示。

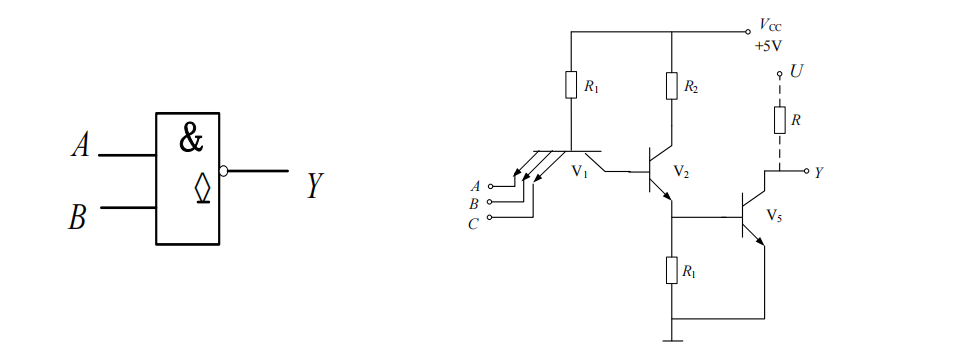

(3)集电极开路的门电路(OC门)

◼ 电路结构

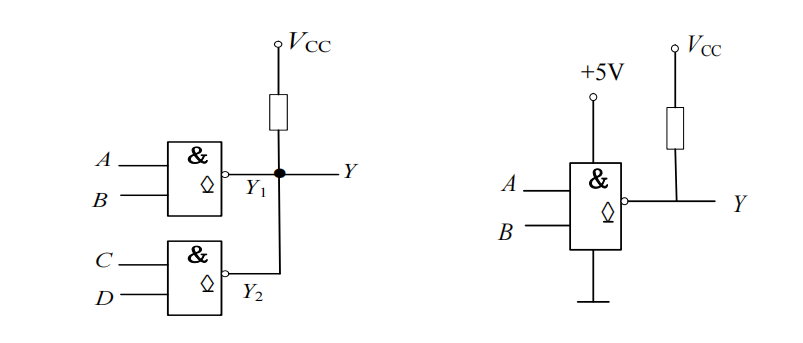

(4)集电极开路门(OC门)的应用

◼ 实现线与逻辑

◼ 组成的电平转换电路

Part.03

组合逻辑电路

(1)基本逻辑运算

◼ 逻辑代数的运算优先顺序是:先算括号,再算非运算,然后是与运算,最后是或运算。逻辑代数运算的规则有:1.代入规则 2.反演规则3.对偶规则

(2)逻辑函数的表示方法

◼ 1.逻辑表达式 2.真值表 3.卡诺图 4.逻辑图 5.波形图

(3)逻辑函数的最小项表达式

◼ 如一个与或逻辑表达式中的每一个与项都是最小项,则该逻辑表达式称作标准与或式,又称为最小项表达式。

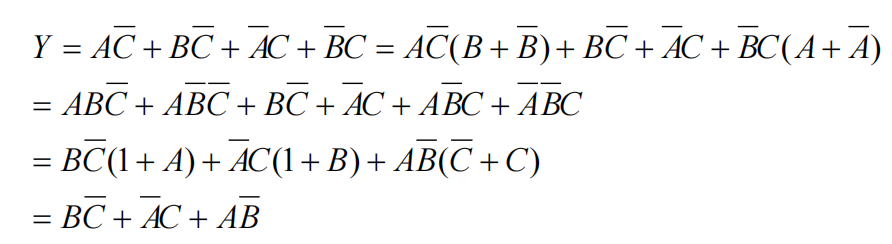

◼ 公式法化简逻辑函数

运用逻辑代数的基本定律和公式对逻辑函数式进行化简的方法称为代数化简法,基本方法有以下几种:1.并项法 2.吸收法 3.消去法 4.配项法

◼ 在不能直接运用公式、定律化简时,可通过乘

或进行配项后再化简。

例如:

(4)卡诺图法化简逻辑函数

◼ 相邻最小项

如果两个最小项中只有一个变量为互反变量,其余变量均相同时,则这两个最小项为逻辑相邻,并把它们称为相邻最小项,简称相邻项。

◼ 卡诺图

卡诺图又称为最小项方格图。用2n个小方格表示n个变量的2n个最小项,并且使相邻最小项在几何位置上也相邻,按这样的相邻要求排列起来的方格图叫做n个变量最小项卡诺图,这样相邻原则又称为卡诺图的相邻性。

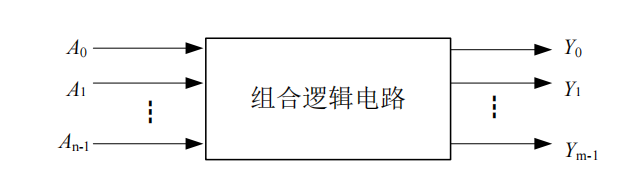

(5)组合逻辑门电路

◼ 组合逻辑电路的基本概念:

在数字逻辑电路中,如果一个电路在任何时刻的输出状态只取决于该时刻的输入状态,而与电路的原有状态无关,则该电路称为组合逻辑电路。

◼ 组合逻辑电路分析:

1.由给定逻辑电路写出其输出逻辑函数表达式。

2.对输出逻辑表达式进行化简。

3.根据输出逻辑表达式列真值表。

4.说明逻辑电路的功能。

◼ 组合逻辑电路的设计:

1.分析设计要求,列真值表。

2.根据真值表写出逻辑表达式。

3.化简逻辑表达式。

4.根据逻辑表达式画出逻辑电路图。

(6)组合逻辑电路中的竞争冒险

◼ 竞争与冒险现象

在组合逻辑电路中,把信号在网络中传输存在时差的现象称为“竞争”。大多数组合逻辑电路都存在竞争,但有的竞争并无害处,而有的竞争会使真值表所述的逻辑关系遭到短暂的破坏,并在输出产生尖峰脉冲(毛刺),这种现象称为产生竞争—冒险。逻辑竞争产生的冒险现象也称逻辑险象。

◼ 逻辑险象的消除方法

1.通过增加冗余项:使函数在任何情况下都不可能出现和的情况,从而达到消除险象的目的。

2.加选通脉冲:对输出可能产生尖峰干扰脉冲的门电路增加一个选通信号的输入端,只有在输入信号转换完成并稳定后,才引入选通脉冲将它打开,此时才允许有输出。

3.接入滤波电容:由于尖峰干扰脉冲的宽度一般都很窄,在可能产生尖峰干扰脉冲的门电路输出端与地之间接入一个容量为几十皮法的电容就可吸收掉尖峰脉冲。

项目实施

项目设计

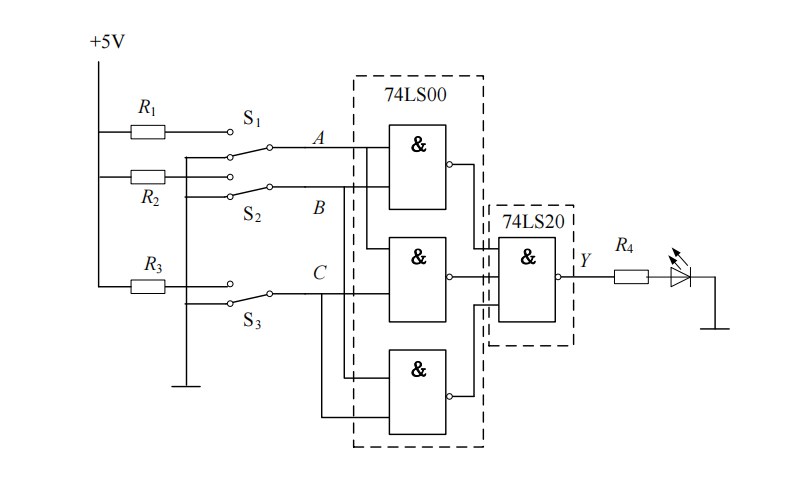

◼ 根据项目要求,设计一个三人多数表决组合逻辑电路。

◼ 分析设计要求。设三人为A、B、C,同意为1,不同意为0;表决为Y,有2人或2人以上同意,表决通过,通过为1,否决为0。因此,A、B、C为输入量,Y为输出量。

◼ 列出真值表

◼ 写出最小项表达式

项目制作

◼ 根据设计逻辑电路,画出三人表决器电路

电路安装

◼ 将检测合格的元器件按照图2-19所示电路连接安装在面包板或万能电路板上。

◼ 插接集成电路时,先校准两排引脚,与底板上插孔对应,然后在确定引脚与插孔吻合后,再稍用力将其插紧。

◼ 导线应粗细适当,一般选取直径为0.6~0.8mm的单股导线,最好用不同色线以区分同用途。

◼ 布线应有次序地进行,随意乱接容易造成漏接或接错,较好的方法是接好固定电平点,其次,按信号源的顺序从输入到输出依次布线。

◼ 连线应避免过长,避免从集成元件上方跨越,避免多次的重叠交错。

◼ 电路布线应整齐、美观、牢固。

实践出真知

学习了这么多理论知识

何不亲自动手实践一番

知行合一

学海方渡

• end •

编辑|刘灿

来源|电气学院分团委学生会科技部

责编|雷芷欣 刘心怡

审核|田孟萍

终审|周巍

投稿邮箱 | eiesu@qq.com

“电光火时”微信编辑团队荣誉出品

好看的人都点了好看??