点击蓝字 关注我们

(报告出品方/作者:华金证券,孙远峰、王海维)

HBM—突破“内存墙”

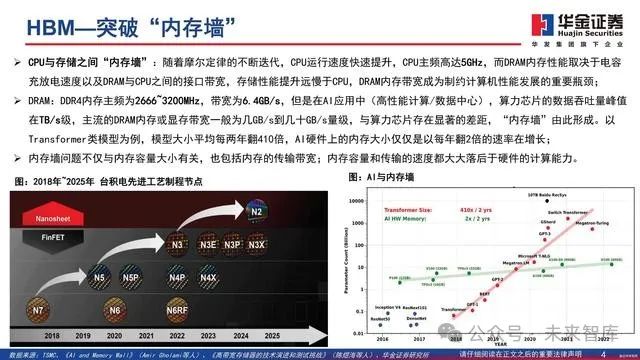

CPU与存储之间“内存墙” :随着摩尔定律的不断迭代,CPU运行速度快速提升,CPU主频高达5GHz,而DRAM内存性能取决于电容充放电速度以及DRAM与CPU之间的接口带宽,存储性能提升远慢于CPU,DRAM内存带宽成为制约计算机性能发展的重要瓶颈;

DRAM:DDR4内存主频为2666~3200MHz,带宽为6.4GB/s,但是在AI应用中(高性能计算/数据中心),算力芯片的数据吞吐量峰值在TB/s级,主流的DRAM内存或显存带宽一般为几GB/s到几十GB/s量级,与算力芯片存在显著的差距,“内存墙”由此形成。以Transformer类模型为例,模型大小平均每两年翻410倍,AI硬件上的内存大小仅仅是以每年翻2倍的速率在增长;

内存墙问题不仅与内存容量大小有关,也包括内存的传输带宽;内存容量和传输的速度都大大落后于硬件的计算能力。

DRAM概念

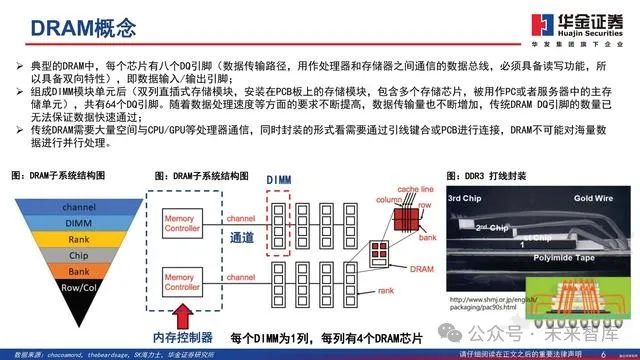

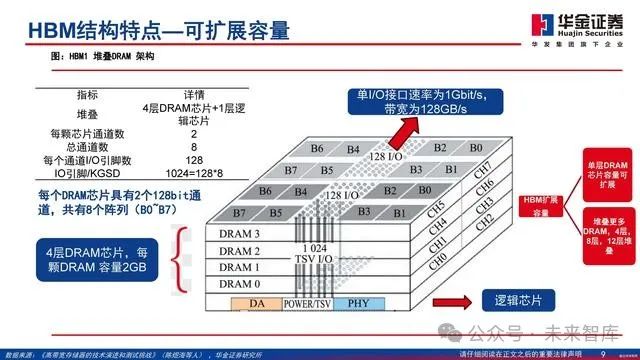

典型的DRAM中,每个芯片有八个DQ引脚(数据传输路径,用作处理器和存储器之间通信的数据总线,必须具备读写功能,所以具备双向特性),即数据输入/输出引脚;

组成DIMM模块单元后(双列直插式存储模块,安装在PCB板上的存储模块,包含多个存储芯片,被用作PC或者服务器中的主存储单元),共有64个DQ引脚。随着数据处理速度等方面的要求不断提高,数据传输量也不断增加,传统DRAM DQ引脚的数量已无法保证数据快速通过;

传统DRAM需要大量空间与CPU/GPU等处理器通信,同时封装的形式看需要通过引线键合或PCB进行连接,DRAM不可能对海量数据进行并行处理。

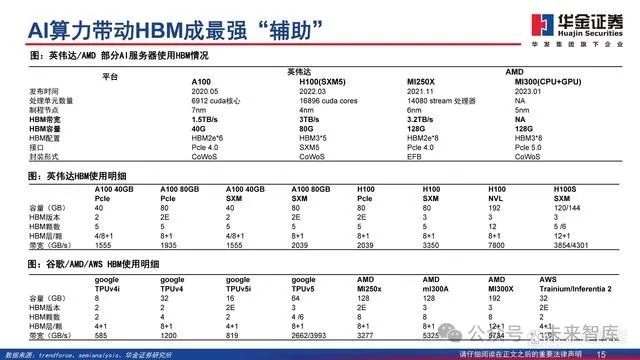

AI算力快速迭代,HBM为最强辅助

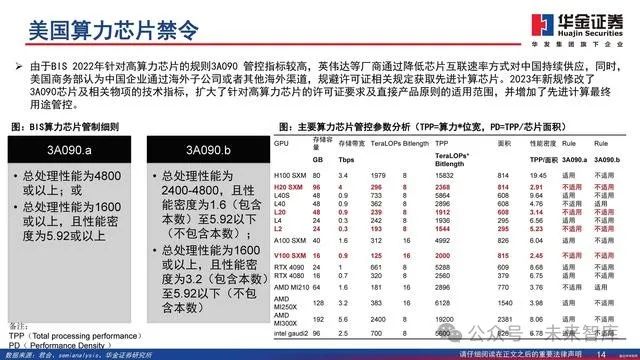

美国算力芯片禁令

由于BIS 2022年针对高算力芯片的规则3A090 管控指标较高,英伟达等厂商通过降低芯片互联速率方式对中国持续供应,同时,美国商务部认为中国企业通过海外子公司或者其他海外渠道,规避许可证相关规定获取先进计算芯片。2023年新规修改了3A090芯片及相关物项的技术指标,扩大了针对高算力芯片的许可证要求及直接产品原则的适用范围,并增加了先进计算最终用途管控。

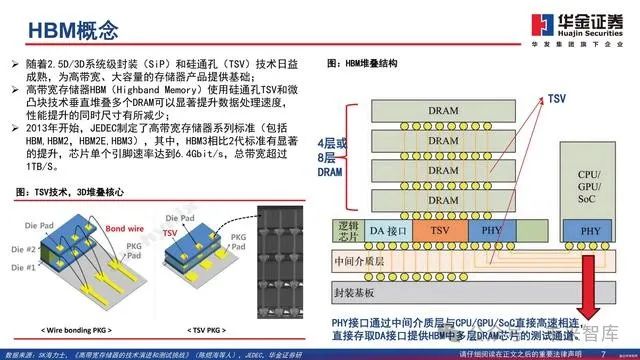

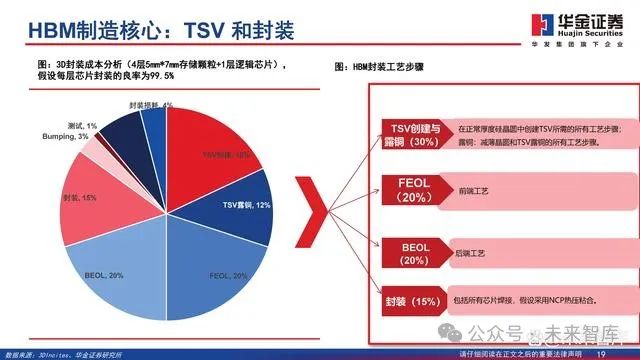

HBM核心—“连接”与“堆叠”,3D混合键合成趋势

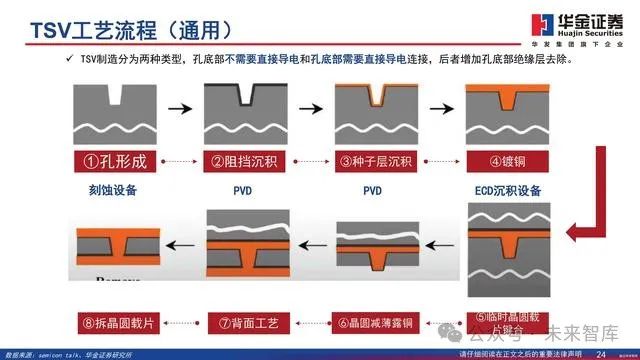

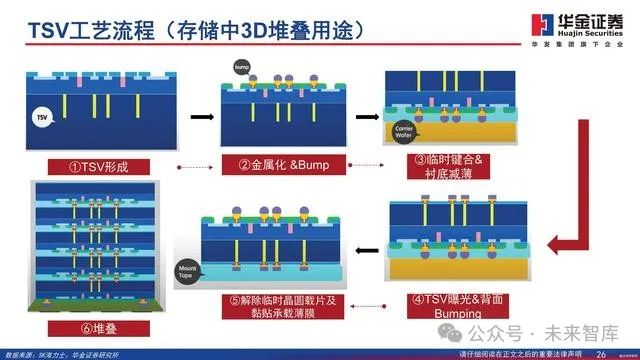

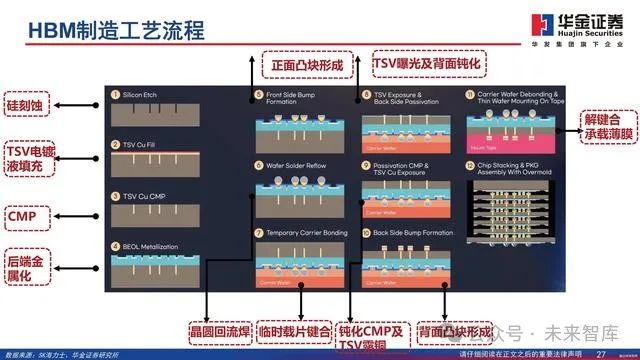

TSV工艺流程(通用)

TSV制造分为两种类型,孔底部不需要直接导电和孔底部需要直接导电连接,后者增加孔底部绝缘层去除。

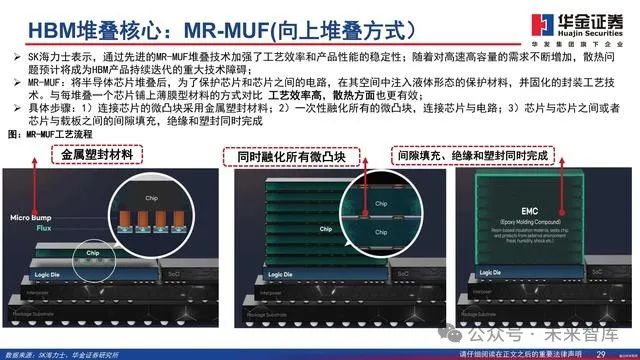

HBM堆叠核心:MR-MUF(向上堆叠方式)

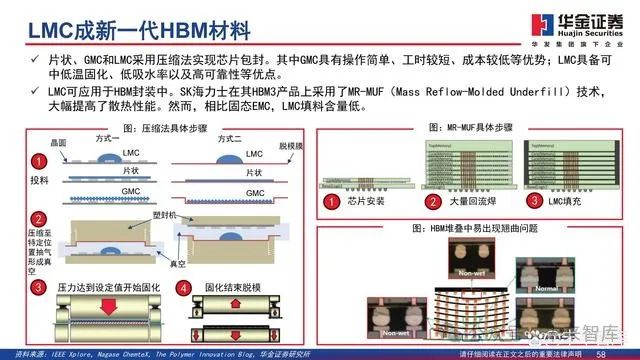

SK海力士表示,通过先进的MR-MUF堆叠技术加强了工艺效率和产品性能的稳定性;随着对高速高容量的需求不断增加,散热问题预计将成为HBM产品持续迭代的重大技术障碍;

MR-MUF:将半导体芯片堆叠后,为了保护芯片和芯片之间的电路,在其空间中注入液体形态的保护材料,并固化的封装工艺技术。与每堆叠一个芯片铺上薄膜型材料的方式对比 工艺效率高,散热方面也更有效;

具体步骤:1)连接芯片的微凸块采用金属塑封材料;2)一次性融化所有的微凸块,连接芯片与电路;3)芯片与芯片之间或者芯片与载板之间的间隙填充,绝缘和塑封同时完成。

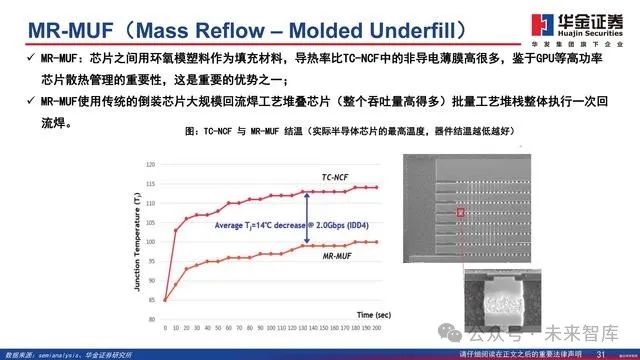

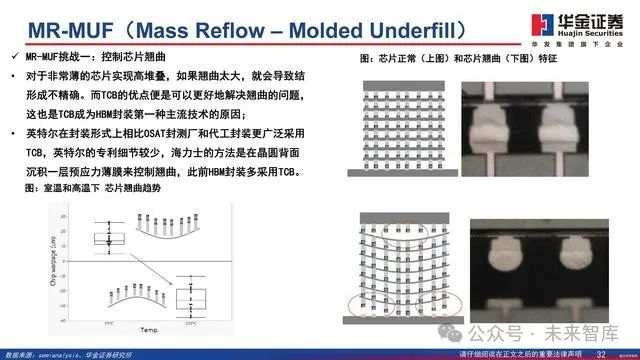

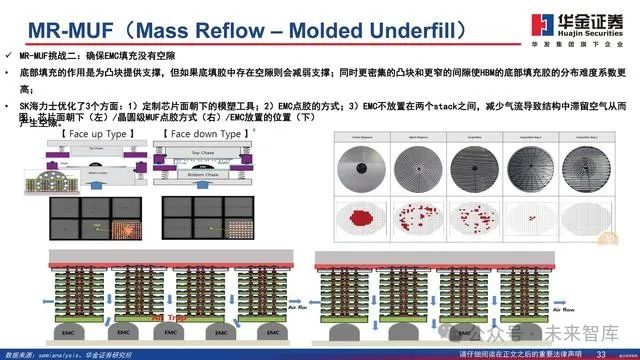

MR-MUF(Mass Reflow – Molded Underfill)

R-MUF:芯片之间用环氧模塑料作为填充材料,导热率比TC-NCF中的非导电薄膜高很多,鉴于GPU等高功率芯片散热管理的重要性,这是重要的优势之一;MR-MUF使用传统的倒装芯片大规模回流焊工艺堆叠芯片(整个吞吐量高得多)批量工艺堆栈整体执行一次回流焊。

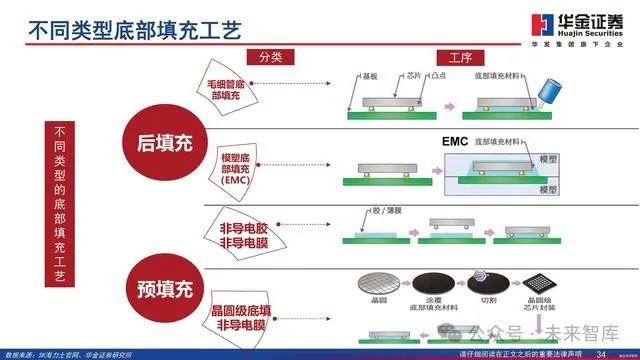

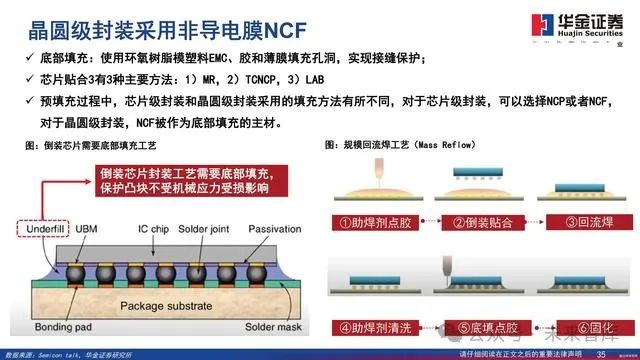

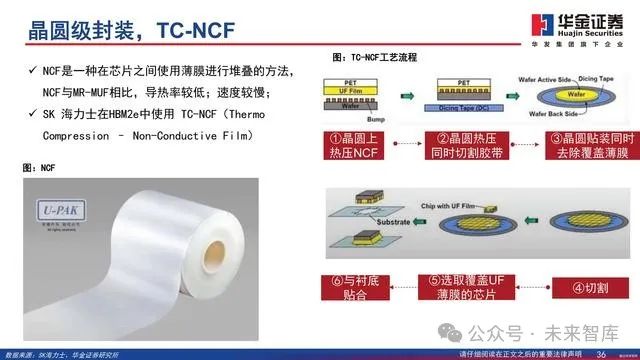

晶圆级封装采用非导电膜NCF

底部填充:使用环氧树脂模塑料EMC、胶和薄膜填充孔洞,实现接缝保护;芯片贴合3有3种主要方法:1)MR,2)TCNCP,3)LAB 。预填充过程中,芯片级封装和晶圆级封装采用的填充方法有所不同,对于芯片级封装,可以选择NCP或者NCF,对于晶圆级封装,NCF被作为底部填充的主材。

HBM测试

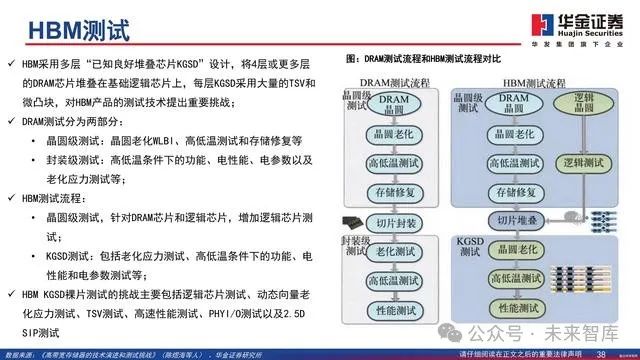

HBM采用多层“已知良好堆叠芯片KGSD”设计,将4层或更多层 的DRAM芯片堆叠在基础逻辑芯片上,每层KGSD采用大量的TSV和 微凸块,对HBM产品的测试技术提出重要挑战;DRAM测试分为两部分:晶圆级测试:晶圆老化WLBI、高低温测试和存储修复等 。封装级测试:高低温条件下的功能、电性能、电参数以及 老化应力测试等;HBM测试流程:晶圆级测试,针对DRAM芯片和逻辑芯片,增加逻辑芯片测 试;KGSD测试:包括老化应力测试、高低温条件下的功能、电 性能和电参数测试等;HBM KGSD裸片测试的挑战主要包括逻辑芯片测试、动态向量老 化应力测试、TSV测试、高速性能测试、PHYI/O测试以及2.5D SIP测试。

HBM核心设备材料,替代进行时

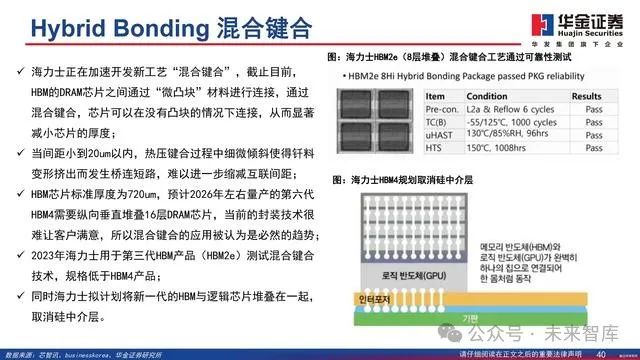

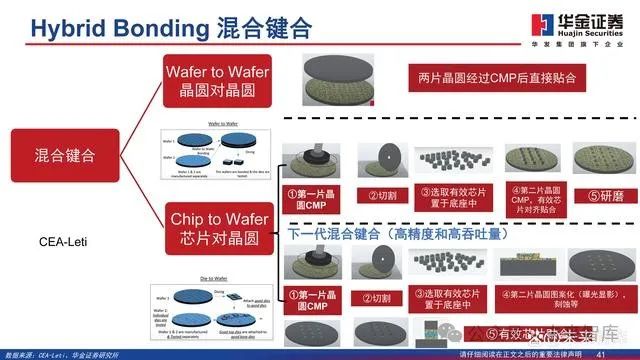

Hybrid Bonding 混合键合

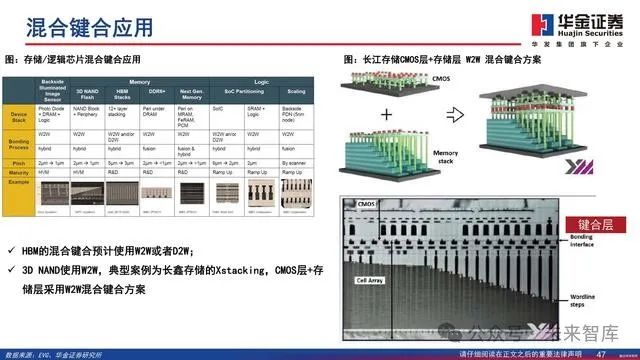

海力士正在加速开发新工艺“混合键合” ,截止目前, HBM的DRAM芯片之间通过“微凸块”材料进行连接,通过 混合键合,芯片可以在没有凸块的情况下连接,从而显著 减小芯片的厚度;当间距小到20um以内,热压键合过程中细微倾斜使得钎料 变形挤出而发生桥连短路,难以进一步缩减互联间距;HBM芯片标准厚度为720um,预计2026年左右量产的第六代 HBM4需要纵向垂直堆叠16层DRAM芯片,当前的封装技术很 难让客户满意,所以混合键合的应用被认为是必然的趋势;2023年海力士用于第三代HBM产品(HBM2e)测试混合键合 技术,规格低于HBM4产品;同时海力士拟计划将新一代的HBM与逻辑芯片堆叠在一起, 取消硅中介层。

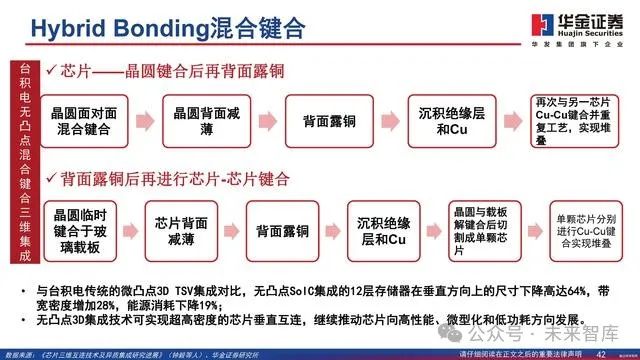

Hybrid Bonding混合键合

与台积电传统的微凸点3D TSV集成对比,无凸点SoIC集成的12层存储器在垂直方向上的尺寸下降高达64%,带宽密度增加28%,能源消耗下降19%;无凸点3D集成技术可实现超高密度的芯片垂直互连,继续推动芯片向高性能、微型化和低功耗方向发展。

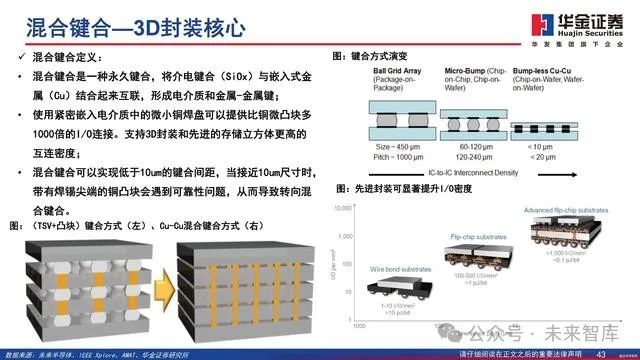

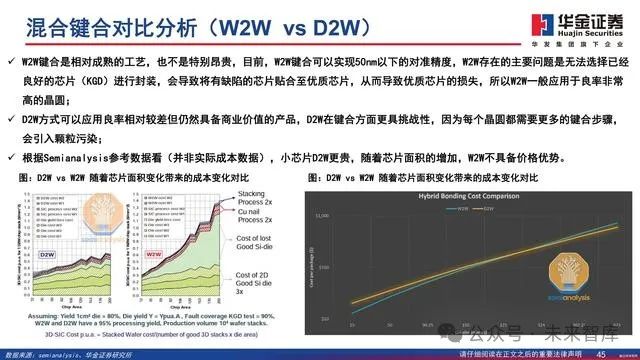

混合键合对比分析(W2Wvs D2W)

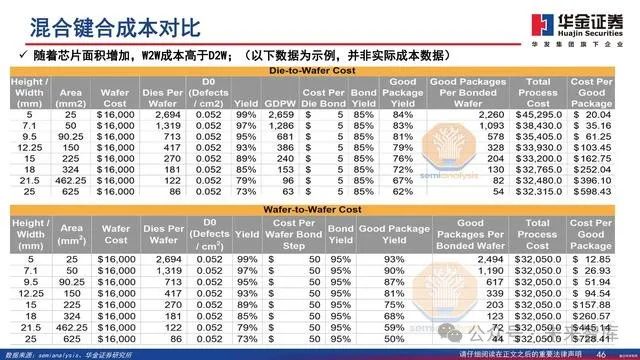

W2W键合是相对成熟的工艺,也不是特别昂贵,目前,W2W键合可以实现50nm以下的对准精度,W2W存在的主要问题是无法选择已经良好的芯片(KGD)进行封装,会导致将有缺陷的芯片贴合至优质芯片,从而导致优质芯片的损失,所以W2W一般应用于良率非常高的晶圆;D2W方式可以应用良率相对较差但仍然具备商业价值的产品,D2W在键合方面更具挑战性,因为每个晶圆都需要更多的键合步骤,会引入颗粒污染;根据Semianalysis参考数据看(并非实际成本数据),小芯片D2W更贵,随着芯片面积的增加,W2W不具备价格优势。

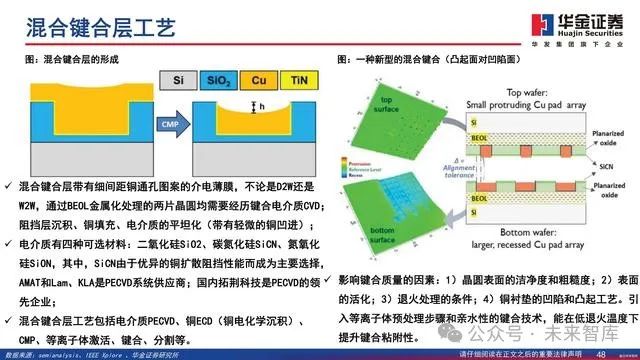

混合键合层工艺

混合键合层带有细间距铜通孔图案的介电薄膜,不论是D2W还是 W2W,通过BEOL金属化处理的两片晶圆均需要经历键合电介质CVD;阻挡层沉积、铜填充、电介质的平坦化(带有轻微的铜凹进);电介质有四种可选材料:二氧化硅SiO2、碳氮化硅SiCN、氮氧化 硅SiON,其中,SiCN由于优异的铜扩散阻挡性能而成为主要选择, AMAT和Lam、KLA是PECVD系统供应商;国内拓荆科技是PECVD的领 先企业;混合键合层工艺包括电介质PECVD、铜ECD(铜电化学沉积)、 CMP、等离子体激活、键合、分割等。

影响键合质量的因素:1)晶圆表面的洁净度和粗糙度;2)表面的活化;3)退火处理的条件;4)铜衬垫的凹陷和凸起工艺。引入等离子体预处理步骤和亲水性的键合技术,能在低退火温度下提升键合粘附性。

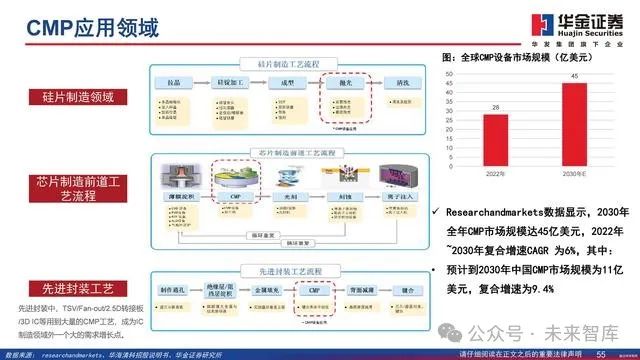

减薄与CMP集成化趋势

晶圆减薄能去除晶圆背面多余的基体材料,进而减小芯片封 装体积、提高芯片散热效率和电气性能,是实现3D集成电路 制造的关键技术之一,例如3D IC中晶圆的键合工艺,减薄是 必要的工序;晶圆在被磨削减薄后需要再经过CMP处理,从而获得表面光滑 平整的晶圆。但是当晶圆被减薄到150um以下时,传输搬运成 为较大风险,尤其是300mm大尺寸规格晶圆物理特性更脆弱。磨削和CMP设备的集成可以减少晶圆的搬运次数,先进封装中 减薄设备正在向集成化、一体化的方向发展;此前国内先进封装减薄设备基本被国外垄断,日本迪斯科和 日本东京精密。2021年9月,华海清科研发的首台12英寸超精 密晶圆减薄机Versatile-GP 300正式出机,集精密硅片背面 磨削减薄、化学机械抛光、硅片清晰功能于一体的专用硅片 减薄设备,可满足集成电路先进制程中的超精密晶圆减薄工 艺需求。

重点公司分析

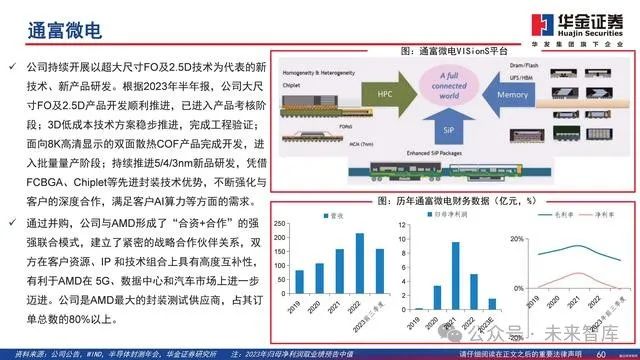

通富微电

公司持续开展以超大尺寸FO及2.5D技术为代表的新 技术、新产品研发。根据2023年半年报,公司大尺 寸FO及2.5D产品开发顺利推进,已进入产品考核阶 段;3D低成本技术方案稳步推进,完成工程验证;面向8K高清显示的双面散热COF产品完成开发,进 入批量量产阶段;持续推进5/4/3nm新品研发,凭借 FCBGA、Chiplet等先进封装技术优势,不断强化与 客户的深度合作,满足客户AI算力等方面的需求。

通过并购,公司与AMD形成了“合资+合作”的强 强联合模式,建立了紧密的战略合作伙伴关系,双方在客户资源、IP 和技术组合上具有高度互补性, 有利于AMD在 5G、数据中心和汽车市场上进一步 迈进。公司是AMD最大的封装测试供应商,占其订单总数的80%以上。

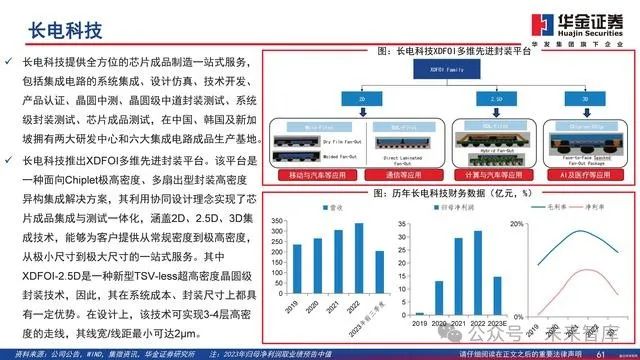

长电科技

长电科技提供全方位的芯片成品制造一站式服务, 包括集成电路的系统集成、设计仿真、技术开发、 产品认证、晶圆中测、晶圆级中道封装测试、系统级封装测试、芯片成品测试,在中国、韩国及新加 坡拥有两大研发中心和六大集成电路成品生产基地。

长电科技推出XDFOI多维先进封装平台。该平台是 一种面向Chiplet极高密度、多扇出型封装高密度 异构集成解决方案,其利用协同设计理念实现了芯 片成品集成与测试一体化,涵盖2D、2.5D、3D集 成技术,能够为客户提供从常规密度到极高密度, 从极小尺寸到极大尺寸的一站式服务。其中 XDFOI-2.5D是一种新型TSV-less超高密度晶圆级 封装技术,因此,其在系统成本、封装尺寸上都具 有一定优势。在设计上,该技术可实现3-4层高密 度的走线,其线宽/线距最小可达2μm。

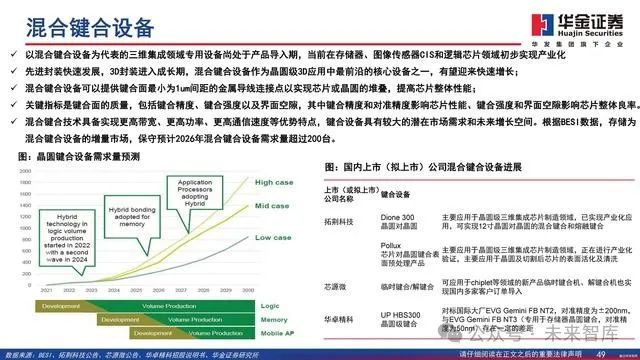

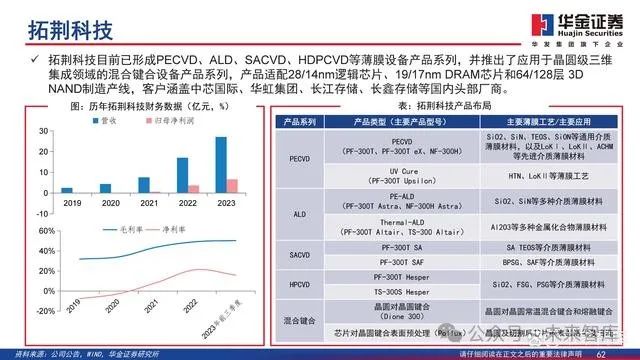

拓荆科技

拓荆科技目前已形成PECVD、ALD、SACVD、HDPCVD等薄膜设备产品系列,并推出了应用于晶圆级三维集成领域的混合键合设备产品系列,产品适配28/14nm逻辑芯片、19/17nm DRAM芯片和64/128层3DNAND制造产线,客户涵盖中芯国际、华虹集团、长江存储、长鑫存储等国内头部厂商。

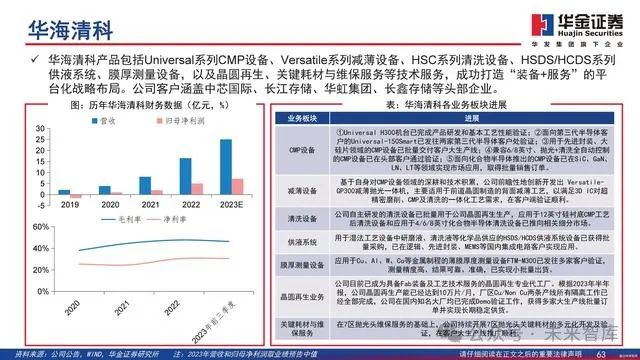

华海清科

华海清科产品包括Universal系列CMP设备、Versatile系列减薄设备、HSC系列清洗设备、HSDS/HCDS系列供液系统、膜厚测量设备,以及晶圆再生、关键耗材与维保服务等技术服务,成功打造“装备+服务”的平台化战略布局。公司客户涵盖中芯国际、长江存储、华虹集团、长鑫存储等头部企业。

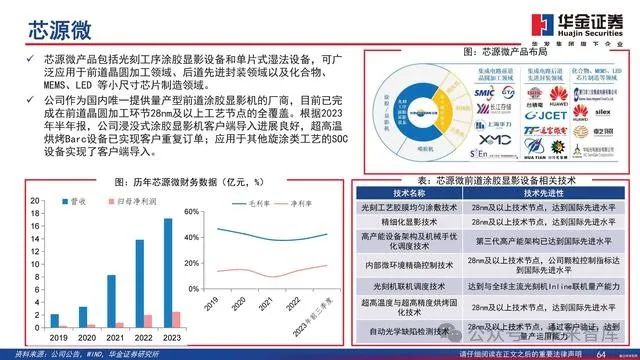

盛美上海

盛美上海掌握了SAPS兆声波清洗技术、无应力抛光技术等多项核心技术,成功研发出单晶圆及槽式湿法清洗设备、电镀设备、无应力抛光设备、立式炉管设备和前道涂胶显影设备和等离子体增强化学气相沉积设备等多种设备,并致力于为半导体制造商提供定制化、高性能、低消耗的工艺解决方案。

报告节选:

荷小生

大勇若怯·大智若愚

“荷理”关心你关心的❤

“荷理”已开通【留言】功能,欢迎踩印留爪~

快来留言你关心的问题或内容,我们将在后续内容里一一进行探讨解读