在之前做了一些基本的市场情况介绍后,⑧蜀也准备做一些简单的技术介绍。

对于芯片制造和设计,大家最常听见的便是“A厂x纳米”这样的叫法,比如高通5纳米和台积电3纳米这样的讲法,那这x纳米究竟是什么意思呢?

首先我们要明白,半导体或者芯片之间有许多种类,多少纳米对于不同种类的芯片未必都是有意义的。通常,我们所指的x纳米芯片,在没有特别说明的情况下,都是特指逻辑芯片所处的技术节点(Technology node),存储芯片则使用另一套技术节点的方法。

在平面晶体管时代,存储芯片和逻辑芯片的技术节点基本相同,都是特指最小结构的半周期(half pitch, HP),此时逻辑芯片的栅极长度(gate length)同半周期是保持一致的。当技术节点到达45纳米以下时,逻辑芯片的HP和栅极长度不再相同,因此通常技术节点特指栅极长度。当平面晶体管在28纳米时代走向重点,3D的FinFET的时代来到时,技术节点甚至与栅极长度都不再保持一致!此时,x纳米就仅仅是一个符号,代表对比平面晶体管等效于栅极长度为x纳米的晶体管密度。所以,出现了台积电7纳米工艺的晶体管密度不如英特尔10纳米工艺的情形。

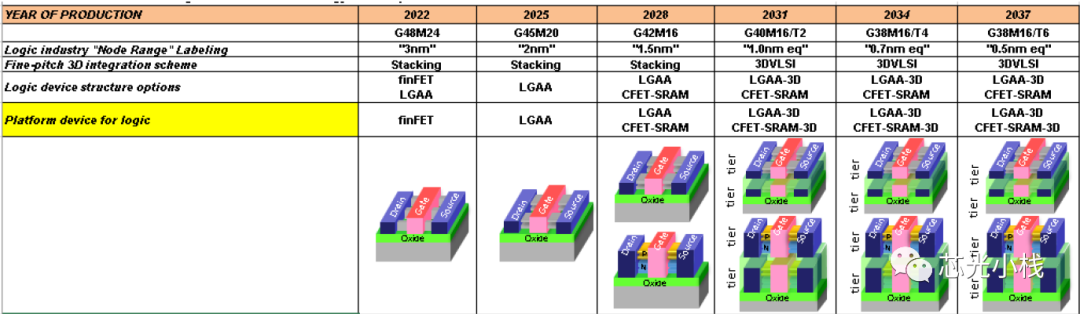

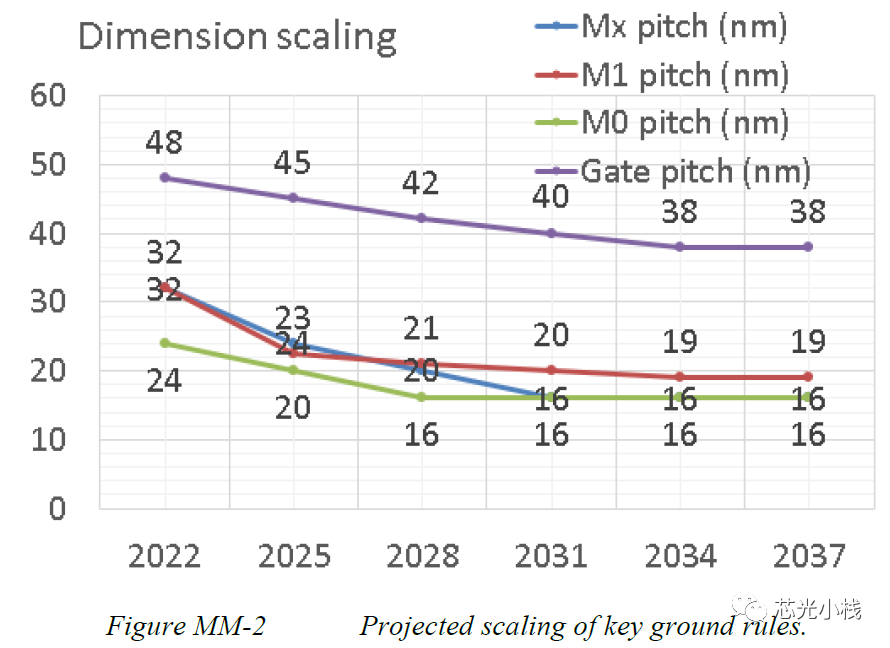

Source: INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS™ (MORE MOORE), IEEE, 2022

上图是2022年,IEEE发布的半导体技术路线图,算是对半导体产业发展的指导性技术文件。这里对应2022~2037分别是3纳米到等效0.5纳米工艺,全周期的栅极周期分别为24~16纳米。在等效0.5纳米时此时的栅极长度大约为8~10纳米,也是下一代high NA EUV光刻机的极限分辨率。因此,28纳米以下时,x纳米仅仅是一个商品牌号而已,与实际栅极长度相比,颇有虚标牌号之嫌。

在去年10月7日美国对中国发布的技术禁运中,对先进制程的芯片的定义为28纳米一下的逻辑芯片,19纳米以下的动态随机存储(DRAM)芯片和128层以上的闪存(3D NAND)芯片。那这里DRAM的19纳米又是什么意思呢?

就像⑧蜀之前所说,存储芯片的技术节点是其最小结构的HP尺寸,这里也没有任何改变,所以DRAM的x纳米,是实实在在的真实物理尺寸。不同厂家对自己的DRAM标号也各不相同,如三星的1x/y/z和1a/b/c,以及美光的1α/β/γ,这些都是特指10纳米级别下不同尺寸。较为早的,也有2x和3x一类的产品,以及下一代的0a和0b产品,相信小伙伴们也能理解其含义。三星的1a使用EUV光刻工艺,实现了14纳米的宽度,而美光则继续使用浸润式光刻工艺在1β达到了12纳米的宽度,这都是目前业界最先进的量产技术。

而对于类似功率芯片和微机电系统这样的芯片,通常使用65纳米甚至0.13微米的工艺就可以制作,但因为功能和应用场景不同,所以技术节点的概念对其根本没有意义。但这并不代表落后,抛开应用场景比较技术节点的做法,基本就是耍流氓。以IGBT为例,其工作电压从数十伏特至上千伏特不等,对于工作电压仅有0点几伏的手机处理器来说,根本无法进行横向比较。

Source: 网络图片

在理解了这些基本概念后,再回过头来看中国的半导体制造,⑧蜀认为,首先实现28纳米以上的完全去美化以及国产化是第一要务!14纳米以及7纳米的大多数光刻层的图形尺寸与28纳米相差并不大,甚至5纳米以下的工艺也有一些层可以适用浸润式光刻技术的工艺,因此深度挖掘浸润式光刻的潜力非常重要,在此基础上依靠EUV光刻才可锦上添花。

不要被3纳米吓破胆,也不要对7纳米沾沾自喜,戒骄戒躁,砥砺前行!我们的5纳米并不遥远,还会用0.13微米打掉美国小院高墙的技术护城河!